# DESIGN OF 4-BIT MULTIPLEXER USING SUB-THRESHOLD ADIABATIC LOGIC (STAL)

### Yuvaraj P.<sup>1</sup>, Rajendran T.<sup>1</sup>, Kamalraj Subramaniam<sup>2</sup>

Department of Electronics and Communication Engineering, Faculty of Engineering, Karpagam University, Coimbatore, Tamil Nadu, India <sup>1</sup>cheranyuvaraj@gmail.com, <sup>1</sup>arajrajesh1990@gmail.com & <sup>2</sup>kamalrajece@gmail.com

### ABSTRACT

**Objective:** This paper presents the low power consumption for Very Large Scale Integration (VLSI) design. The dynamic power consumption of CMOS circuits is continuously becoming a major concern in VLSI technique. **Tool:** All the simulations in this work are done using Tanner EDA Tools V14.11. **Contribution & Results:** In this paper the 4-Bit STAL multiplexer design have been analyzed and low power multiplexer is designed using the positive feedback logic. The STAL multiplexer is a Positive Feedback-STAL consumes less power than the CMOS multiplexer is identified from this study. **Applications:** In mere future the system can be enhanced to perform higher order bits.

Keywords— CMOS, multiplexer, power consumption, VLSI, STAL, Positive Feedback STAL.

### I. INTRODUCTION

The major objective of this work is to provide an optimal solution for the VLSI low power designers. This work mainly focuses on the minimizing of the total power dissipation, which results in a rapid growth with the scaling down of the technologies. Several techniques at the various levels of the design process have been implemented to reduce the total power dissipation in the circuit, architectural as well as the system level. Additionally, the number of gates per chip area is constantly increasing, while the gate switching of the circuit's total energy does not decrease at the same rate, such results in the rise of power dissipation and heat transfer becomes more complicated and expensive. Then, to curb the power dissipation, a substitute solution at each levels of abstraction is proposed. The dynamic power demand of CMOS circuits is rapidly fetching a crucial concern in the design of distinctive information systems and large computers. In this proposed work, a new CMOS logic family called SUB-THRESHOLD ADIABATIC LOGIC, based on the STAL switching principle is presented for the design of 4-Bit multiplexer. The term STAL originates from thermodynamics, which is used to denote a process in which there is no transfer of heat with the surroundings. The STAL logic structure substantially reduces the power dissipation. The Sub-Threshold Adiabatic switching technique can achieve very low power Dissipation, but at the extortionate of circuit complexity. STAL proffers a way to reuse the energy hoarded in the load capacitors rather than the conventional way of discharging the load capacitors to the ground. Thus, minimum power consumption during charge transfer phase known as STAL switching has been studied from the literatures. Conventional CMOS based designs consume a lot of energy during switching process. STAL switching technique reduces the energy dissipation through PMOS during charging process and reuses the energy stored on the load capacitor during discharging. It consists of two cross-coupled transistors M1 and M2 as load devices and two NMOS transistors in the functional unit. It processes and produce complementary inputs and outputs.

### II. SUB THRESHOLD ADIABATIC LOGIC DESIGN

The STAL is a Positive Feedback Adiabatic Logic (PFAL) structure, which reduces the power dissipation

in an overdramatizing manner. The STAL switching scheme is used to achieve low power dissipation, in exorbitant of circuit complexity. STAL logic proffer a path to reuse the energy deposited in the load capacitors preferably the traditional way of discharging the load capacitors to the ground<sup>1</sup>. It should be well known that the fully STAL operation of the circuit is a consummate condition which may be approached linearly as the STAL switching process is reversed down. In most of the cases, the dissipation in energy corresponding with a charge transfer event is usually collected of a STAL component and a non-Sub-Threshold Adiabatic Logic (nSTAL) component. Therefore, reducing all the energy loss to zero is highly impossible, nevertheless of the switching speed. With the STAL switching approach, the circuit energies are perpetuated preferably than dissipated as heat.

Depending on the practical applications and the requirements, this approach can sometimes be used to reduce the power dissipation of the digital systems <sup>2-5</sup>. Like many other STAL logic families, Reversible logic is a dual-rail logic family constructed especially on a pair of cross-coupled inverters that are supplied using a power-clock, other than static DC power supply. The layout of the appraisal logic is what makes reversible logic an ideal family to implement fully reversible STAL logic<sup>6</sup>. This logic is constructed from nMOS devices are connected between the power-clock and the outputs. These nMOS devices take complementary inputs and are constructed to fabricate a low-resistance track between the power-clock and the asserted output. The non-asserted output should be left with a highimpedance track to power-clock, and will be heaved low by the cross-coupled n-type devices. This means that the function is evaluated when there is sufficient differential between the two outputs, but far more importantly means that by using reverse-flowing data, the outputs can be more completely recovered. This should allow losses to be reduced to leakage. 7-9

### **III. DESIGN & IMPLEMENTATION**

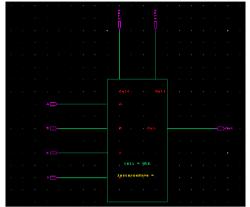

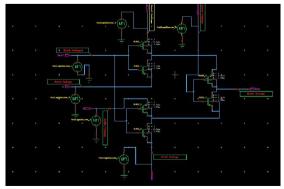

All the circuits are verified with several input combination and load capacitor, in Tanner EDA Tool V.14.11. Positive Feedback Sub-Threshold Adiabatic Logic (PF-STAL) Logic is a semi STAL approach which tries to increase the charging and discharging times maintaining the swing levels. It requires presence of dual nature of input (complemented and un-complemented) and creates dual nature for the output. PF-STAL logic shows very positive aspects in addressing the power issues<sup>10-13</sup>. PF-STAL comes in dual rail logic family which requires both the complementary and Uncomplimentary inputs for the logic function<sup>14-17</sup> (Refer Figure 1 to 4).

The Logic function (F) and (F bar) are implementted using NMOS networks alongside the two cross coupled inverts as latch known as sense amplifier which drives the two complementary outputs of the circuit. It consists of two PMOS and two NMOS switches which ultimately prevents the output terminals from degradation of logic levels. One of the logic blocks connects the concerned input to the power clock with a low resistance path and on the same time the other function provides a very high resistance in between the power clock and the other concerned output. But the inverter's network provides the second output a conducting path to the ground. In this way one of the two outputs differrent is pulled up to the power clock and other down to the ground<sup>14-17</sup> (Refer Figure 1 to 4).

# a. Conventional and Sub-Threshold Adiabatic Logic (STAL) addressing

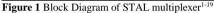

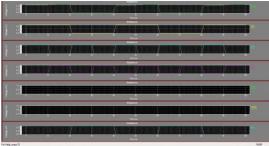

In this technique, the energy dissipation of the CN and CCN reversible logic gates are scrutinized for two different logic switching methods. The first, traditional logic switching, is a simulation of the energy dissipateion performance for a range of different input signal rise and fall times ( $\tau$ ). At the faster speed, this rule becomes equivalent to conventional unrestricted step logic transition. However, as the input logic signal speed is slowed, converting to a ramp function, the Sub-Threshold Adiabatic Logic (STAL) switching principle, can be evaluated. Figure 2 shows a typical input to a CCN gate where the input signal transitions are in the form of a linear ramp function and where V<sub>a</sub>, V<sub>b</sub> and V<sub>c</sub> are the input voltages on the three input signals A, B and C respectively<sup>18</sup> (Refer Figure 5 to 7).

In this technique, only input signals that have a different final input logic signal change state.  $V_a$  keeps its voltage of +2.5V representing a constant binary 1 while  $V_c$  keeps its voltage of -2.5V representing a constant binary 0.  $V_b$  moves from -2.5 V to +2.5V as a linear ramp versus time. i.e., changing logic state  $0 \rightarrow 1$ . The Sub-Threshold Adiabatic Logic (STAL) addressing is yet another switching method that is also used while investigating the performance for energy dissipation of the Controlled Not (CN) and Controlled Controlled Not (CCN) gates<sup>18-19</sup> (Refer Figure 5 to 7).

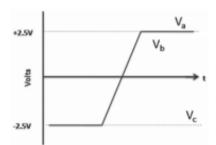

A set of i/p logic switching waveforms for a and Controlled Not (CN) gate when executing through Sub-Threshold Adiabatic Logic (STAL) addressing. Where  $V_a$ ,  $V_b$  and  $V_c$  are the input voltages associated with the three inputs A, B and C respectively shown in Figure 3. The input logic switching transition sequence consists of two phases. In the first phase, all input signals move to the midpoint voltage of 0 volts with a controlled rise time / fall ( $\tau$ ) time (see  $V_a$ ,  $V_b$ ,  $V_c$ ,  $t_{rise} = t_{fall} = T/2$ , for t <  $t_{midpoint}$ ). In the second phase, input signals move either to their new logic state or back to their original logic state (see V<sub>a</sub>,V<sub>b</sub>,V<sub>c</sub>, t<sub>rise</sub> = t<sub>fall</sub> = T/2, for t > t<sub>midpoint</sub>). V<sub>b</sub> moves from -2.5 to +2.5 i.e. changing logic state 0 $\rightarrow$ 1. V<sub>a</sub> moves from +2.5 to 0 and back to + 2.5 i.e. maintaining logic state 1. V<sub>c</sub> moves from -2.5 to 0 and back to - 2.5 i.e. maintaining logic state 0<sup>18-19</sup> (Refer Figure 5 to 7).

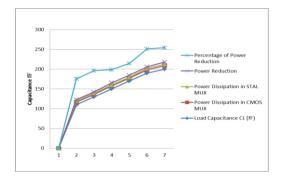

### IV. RESULTS AND DISCUSSION ON THE BASIS OF POWER

We have designed and simulated 4-Bit Multiplexers based on static CMOS and STAL. But this simulation is based on constant load capacitance, constant frequency and constant room temperature<sup>18-19</sup>. But in the real world, multiplexer need to be work on varying parameters and varying conditions. So, now we will observe the effect of varying condition or varying parameters on Static CMOS Multiplexer and Multiplexer based on STAL and observe, why multiplexer based on STAL is better in power savings then Multiplexer based on Static CMOS. The 4- Bit static CMOS Multiplexer and 4- Bit STAL Multiplexer were compared on different varying parameters on the basis of power dissipation across them<sup>18-19</sup> (Refer Figure 5 to 7).

# *i)* Average power consumed by 4-Bit Multiplexer designed with static CMOS family and sub threshold adabatic family for different load capacitance values.

In this section, we have observed the effect of variation in load capacitance over the average power consumed by 4-Bit multiplexer based on Static CMOS and STAL<sup>18-19</sup>. The load capacitance is varied from 10-Ff-190fF with a step size of 20fF and resulting power consumption is observed. The operating temperature is kept constant i.e 24°C. Input selected are  $D_0=13$ Mhz,  $D_1=8$ Mhz and S=25Mhz. The effect of variation of load capacitance over power dissipation is shown in the table 1<sup>18-19</sup> (Refer Figure 5 to 7).

### V. CONCLUSION

STAL circuits are low power solutions which will soon replace CMOS based logic circuits. From the above results, it is clearly depicted that STAL logic circuits reduce power dissipation with a design size penalty in terms of transistor count. Circuit simulations show that with the help of PFAL, the energy savings can be reached at a significant level. Utilizing the basic PFAL technology basic gates (NAND & NOR) are implemented, verified and analyzed. From the simulations the functionality of the implemented logic gates is found to be satisfactory.

#### VI. FUTURE SCOPE

- The high cost-per-weight of launching computingrelated power supplies, solar panels and cooling systems into orbit imposes a demand for STAL power reduction in spacecraft in which these components weigh a significant fraction of total spacecraft weight.

- Realizing 8-Bit, 16-Bit & 32-Bit multiplexers using 4-Bit multiplexer with the help of STAL families.

- STAL circuits needs non-conventional power supply which causes overhead in terms of area hence overall cost is increased. So, design a new sub threshold adiabatic logic family which can be operated by conventional power supply.

Switching speed of STAL circuit is slow as compare to CMOS logic. So, design a new sub threshold adiabatic family with better switching speed.

## REFERENCES

- Sowjanya M. and Malik S.A., Efficiency of Adiabatic Logic for Low-Power VLSI Using Cascaded ECRL and PFAL Inverter. Int. J. of Engineering Research and Applications (2013).

- [2]. Athas W.C., Svensson L., Koller J.G., Low-power digital systems based on adiabatic-switching principles, IEEE Transactions on Very Large Scale Integration System (1994).

- [3]. A. Vetuli, S. Di Pascoli and L.M. Reyneri, Positive feedback in adiabatic logic. Electron. Lett. (1996)

- [4]. Gaurav Singh, et al., Comparative Analysis of Conventional CMOS and Energy Efficient Adiabatic Logic Circuits. Int. J. of Emerging Technology and Advanced Engg. (2013).

- [5]. David J. Willingham and Izzet Kale, Using Positive Feedback Adiabatic Logic to implement Reversible Toffoli Gates, Westminster Research University of Westminster (2008).

- [6]. Tanuja Jaggi, Ravinder Kumar, Performance Analysis of Positive Feedback Adiabatic Logic for Low Power. Int. J. of Advanced Research in Electrical, Electronics and Instrumentation Engineering (2013).

- [7]. Mukesh Tiwari, et al., Adiabatic Improved Efficient Charge Recovery Logic for low power CMOS logic. Int. J. of Electronic Communication and Computer Engineering (2013).

- [8]. Ettore Amirante, Agnese Bargagli-Stoffi, Jurgen Fischer, Giuseppe Iannaccone, and Doris Schmitt-Landsiedel, Variations of the Power Dissipation in Adiabatic Logic Gates (2013).

- [9]. Willingham, D.J., Kale, I., Using Positive Feedback Adiabatic Logic to implement Reversible Toffoli Gates, NORCHIP (2008).

- [10]. Manoj Sharma & Arti Noor, Positive Feed Back Adiabatic Logic: PFAL Single Edge Triggered Semi-Adiabatic D Flip Flop, African Journal of Basic & Applied Sciences (2013).

- [11]. Richa Singh & Rajesh Mehra, Power Efficient Design of Multiplexer using Adiabatic Logic. Int. J. of Advan. in Engineering & Technology (2013).

- [12]. Zhijin Guan, et. al., An Arithmetic Logic Unit design based on reversible logic gates, Communications, Computers and Signal Processing (2011).

- [13]. Monika Sharma, Design and Analysis of CMOS Cells using Adiabatic Logic (2012).

- [14]. Sanjay Kumar, Design of Low Power CMOS Cell Structures based on Adiabatic Switching Principle, M.Tech Thesis, Thanpar University (2009).

- [15]. Kanika Kaur & Arti Noor, Strategies & Methodologies for Low Power VLSI Designs: A Review. Int. J. Advan. in Engineering & Technol. (2011).

- [16] Tabei, K. & Yamada, T., On generating test sets for reversible circuits, Computer Engineering and Systems (2009).

- [17] W.C.Athas, et al., An energy efficient CMOS line driver using adiabatic switching, IEEE Symp. on

Design Automation of High Performance VLSI Systems (1994).

- [18]. Amit Saxena, et al., Power Efficient Adiabatic Switching Circuits, MIT Int. J. Electronics & Communication Engineering (2013).

- [19]. Deepti Shinghal, et al., Adiabatic Logic Circuits: A Retrospect. MIT Int. J. Electronics & Communication Engineering (2013).

Figure 2 Conventional switching i/p voltage waveforms of CMOS  $MUX^{1-19}$

**Figure 3** I/P voltage waveforms for STAL switching in Multiplexers<sup>1-19</sup>

Figure 4 Circuit of STAL multiplexer

Figure 5 Output Response of STAL MUX

**Figure 6** Performance analysis of power of STAL MUX vs. CMOS MUX

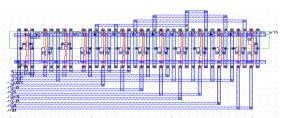

Figure 7 Layout of 4-Bit STAL MUX

| Load        | Power Dissi- | Power          | Power     | Percentage |

|-------------|--------------|----------------|-----------|------------|

| Capacitance | pation in    | Dissipation in | Reduction | of Power   |

| $C_L$ (fF)  | CMOS MUX     | STAL MUX       | μw        | Reduction  |

| 110         | 6.325        | 3.333          | 2.992     | 52.69      |

| 130         | 6.024        | 3.247          | 2.777     | 53.90      |

| 150         | 7.562        | 2.445          | 5.117     | 33.33      |

| 170         | 7.258        | 2.154          | 5.104     | 29.68      |

| 190         | 7.895        | 3.547          | 4.348     | 44.93      |

| 200         | 8.963        | 3.242          | 5.721     | 36.17      |